| 型号 | 品牌 | 描述 | 获取价格 | 数据表 |

| 25CSR-8PK | JST | 这是一个1.0mm螺距绝缘位移连接器与安全锁定结构,以防止脱离连接器和不完全嵌合。1.8A |

获取价格 |

|

| 25CTBB | ADAM-TECH | HEADER & HOUSING SYSTEMS |

获取价格 |

|

| 25CTBR | ADAM-TECH | HEADER & HOUSING SYSTEMS |

获取价格 |

|

| 25CTB-R | ADAM-TECH | HEADER & HOUSING SYSTEMS 2.5mm Type B & C |

获取价格 |

|

| 25CTCB | ADAM-TECH | HEADER & HOUSING SYSTEMS |

获取价格 |

|

| 25CTCR | ADAM-TECH | HEADER & HOUSING SYSTEMS |

获取价格 |

|

pcf8563芯片功能说明、参数分析、引脚说明

pcf8563芯片功能说明、参数分析、引脚说明

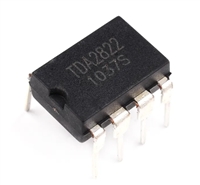

TDA2822资料手册:引脚说明、参数分析

TDA2822资料手册:引脚说明、参数分析

TJA1050资料数据分析、引脚说明、应用示例介绍

TJA1050资料数据分析、引脚说明、应用示例介绍

DS3231时钟芯片:参数分析、引脚说明、应用示例介绍

DS3231时钟芯片:参数分析、引脚说明、应用示例介绍