N01S830HA, N01S830BA

CS

SCK

0

1

2

3

4

5

12 13 14 15 16 17 18 19 20 21 22 23 24 25 26

Instruction

24−bit address

Data out

H0 H0 L0 L0 H1 H1 L1 L1

MSB

C3 C2 C1 C0 A11 A10

A3 A2 A1 A0

X

X

X

X

SIO[1:0]

MSB

Notes:

C[3:0] = 03h

H0 = 2 high order bits of data byte 0

L0 = 2 low order bits of data byte 0

H1 = 2 high order bits of data byte 1

L1 = 2 low order bits of data byte 1

Figure 4. DUAL Read Sequence

CS

SCK

0

1

2

3

4

5

6

7

8

9

10 11 12 13 14 15 16

Instruction

24−bit address

Data out

H0 L0 H1 L1 H2 L2 H3 L3

MSB

SIO[3:0]

C1 C0 A5 A4 A3 A2 A1 A0

MSB

X

X

Notes:

C[1:0] = 03h

H0 = 4 high order bits of data byte 0

L0 = 4 low order bits of data byte 0

H1 = 4 high order bits of data byte 1

L1 = 4 low order bits of data byte 1

Figure 5. QUAD Read Sequence

Write Operation

The serial SRAM WRITE is selected by enabling CS low.

First, the 8-bit WRITE instruction is transmitted to the

device followed by the 24-bit address with the 7 MSBs being

don’t care. After the WRITE instruction and addresses are

sent, the data to be stored in memory is shifted in on the SI

pin.

If operating in page mode, after the initial word of data is

shifted in, additional data words can be written as long as the

address requested is sequential on the same page. Simply

write the data on SI pin and continue to provide clock pulses.

The internal address pointer is automatically incremented to

the next higher address on the page after each word of data

is written in. This can be continued for the entire page length

of 32 words long. At the end of the page, the addresses

pointer will be wrapped to the 0 word address within the

page and the operation can be continuously looped over the

32 words of the same page. The new data will replace data

already stored in the memory locations.

If operating in burst mode, after the initial word of data is

shifted in, additional data words can be written to the next

sequential memory locations by continuing to provide clock

pulses. The internal address pointer is automatically

incremented to the next higher address after each word of

data is read out. This can be continued for the entire array

and when the highest address is reached, 1FFFFh, the

address counter wraps to the address 00000h. This allows

the burst write cycle to be continued indefinitely. Again, the

new data will replace data already stored in the memory

locations.

All WRITE operations are terminated by pulling CS high.

www.onsemi.com

5

74HC245八路双向总线收发器:资料手册参数分析

74HC245八路双向总线收发器:资料手册参数分析

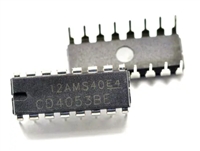

CD4053模拟多路复用器/解复用器:资料手册参数分析

CD4053模拟多路复用器/解复用器:资料手册参数分析

CD4011双4位二进制计数器:资料手册参数分析

CD4011双4位二进制计数器:资料手册参数分析

PCM1794音频DAC:全面参数解析与关键特性指南

PCM1794音频DAC:全面参数解析与关键特性指南