| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| M1033-11-168.0400 | IDT |

获取价格 |

PLL Based Clock Driver, 1033 Series, 1 True Output(s), 0 Inverted Output(s), CQCC36, 9 X 9 |

|

| M1033-11-168.0400LF | IDT |

获取价格 |

PLL Based Clock Driver, 1033 Series, 1 True Output(s), 0 Inverted Output(s), CQCC36, 9 X 9 |

|

| M1033-11-172.6423 | IDT |

获取价格 |

PLL Based Clock Driver, 1033 Series, 1 True Output(s), 0 Inverted Output(s), CQCC36, 9 X 9 |

|

| M1033-11-172.6423LF | IDT |

获取价格 |

PLL Based Clock Driver, 1033 Series, 1 True Output(s), 0 Inverted Output(s), CQCC36, 9 X 9 |

|

| M1033-11I155.5200 | ICSI |

获取价格 |

VCSO BASED CLOCK PLL WITH AUTOSWITCH |

|

| M1033-11I155.5200LF | IDT |

获取价格 |

PLL Based Clock Driver, 1033 Series, 1 True Output(s), 0 Inverted Output(s), CQCC36, 9 X 9 |

|

| M1033-11I156.2500 | ICSI |

获取价格 |

VCSO BASED CLOCK PLL WITH AUTOSWITCH |

|

| M1033-11I156.2500LF | IDT |

获取价格 |

PLL Based Clock Driver, 1033 Series, 1 True Output(s), 0 Inverted Output(s), CQCC36, 9 X 9 |

|

| M1033-11I156.8324 | IDT |

获取价格 |

PLL Based Clock Driver, 1033 Series, 1 True Output(s), 0 Inverted Output(s), CQCC36, 9 X 9 |

|

| M1033-11I161.1328LF | IDT |

获取价格 |

PLL Based Clock Driver, 1033 Series, 1 True Output(s), 0 Inverted Output(s), CQCC36, 9 X 9 |

|

DS1135-8资料手册解读:深入探索高速硅定时电路的特性与应用

DS1135-8资料手册解读:深入探索高速硅定时电路的特性与应用

GT60N321资料手册解读:深入了解东芝第四代绝缘栅双极晶体管

GT60N321资料手册解读:深入了解东芝第四代绝缘栅双极晶体管

STS5DNE30L资料手册解读:参数分析、特性与应用

STS5DNE30L资料手册解读:参数分析、特性与应用

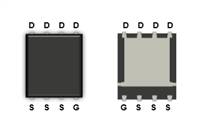

MDU1511资料手册解读:探索这款MOSFET的全面特性

MDU1511资料手册解读:探索这款MOSFET的全面特性