| 型号 | 品牌 | 描述 | 获取价格 | 数据表 |

| DAC1264X_RA | ETC | DAC1264X_RA 3.3V 10BIT 2MSPS DAC|Data Sheet |

获取价格 |

|

| DAC1264X_RA3 | ETC | DAC1264X_RA3 3.3V 10BIT 2MSPS 8-Channel DAC|Data Sheet |

获取价格 |

|

| DAC1265 | NSC | HI-SPEED 12-BIT D/A CONVERTER |

获取价格 |

|

| DAC1265A | NSC | HI-SPEED 12-BIT D/A CONVERTER |

获取价格 |

|

| DAC1265ACJ | NSC | HI-SPEED 12-BIT D/A CONVERTER |

获取价格 |

|

| DAC1265ACJ/A+ | ETC | 12-Bit Digital-to-Analog Converter |

获取价格 |

|

MC34063开关稳压器:全面参数解析与设计指南

MC34063开关稳压器:全面参数解析与设计指南

CC2530无线微控制器:资料手册参数分析

CC2530无线微控制器:资料手册参数分析

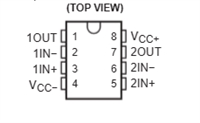

NE5532双低噪声运算放大器:资料手册参数分析

NE5532双低噪声运算放大器:资料手册参数分析

74LS138 3-to-8线解码器/多路复用器:资料手册参数分析

74LS138 3-to-8线解码器/多路复用器:资料手册参数分析