| 型号 | 品牌 | 描述 | 获取价格 | 数据表 |

| AX88782 | ASIX | ASIX Multi-Port Ethernet Controller |

获取价格 |

|

| AX88782LF | ASIX | Micro Peripheral IC |

获取价格 |

|

| AX88783 | ASIX | ASIX Multi-Port Ethernet Controller |

获取价格 |

|

| AX88783LF | ASIX | Micro Peripheral IC |

获取价格 |

|

| AX88790L | ASIX | 10/100BASE 3-in-1 PCMCIA Fast Ethernet Controller |

获取价格 |

|

| AX88796 | ASIX | 3-in-1 Local Bus Fast Ethernet Controller |

获取价格 |

|

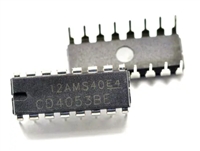

CD4053模拟多路复用器/解复用器:资料手册参数分析

CD4053模拟多路复用器/解复用器:资料手册参数分析

CD4011双4位二进制计数器:资料手册参数分析

CD4011双4位二进制计数器:资料手册参数分析

PCM1794音频DAC:全面参数解析与关键特性指南

PCM1794音频DAC:全面参数解析与关键特性指南

TLP250光耦合器:资料手册参数分析

TLP250光耦合器:资料手册参数分析