| 生命周期: | Transferred | 包装说明: | , DIE OR CHIP |

| Reach Compliance Code: | compliant | ECCN代码: | EAR99 |

| HTS代码: | 8523.59.00.00 | 风险等级: | 5.11 |

| JESD-30 代码: | R-XUUC-N | 功能数量: | 1 |

| 最高工作温度: | 85 °C | 最低工作温度: | -40 °C |

| 封装主体材料: | UNSPECIFIED | 封装等效代码: | DIE OR CHIP |

| 封装形状: | RECTANGULAR | 封装形式: | UNCASED CHIP |

| 认证状态: | Not Qualified | 子类别: | Other Telecom ICs |

| 表面贴装: | NO | 电信集成电路类型: | TELECOM CIRCUIT |

| 温度等级: | INDUSTRIAL | 端子形式: | NO LEAD |

| 端子位置: | UPPER | Base Number Matches: | 1 |

| 型号 | 品牌 | 描述 | 获取价格 | 数据表 |

| ATA5577M1330C-DDW | MICROCHIP | Telecom Circuit |

获取价格 |

|

| ATA5577M1330C-PAE | ATMEL | Telecom Circuit, |

获取价格 |

|

| ATA5577M1330C-PAE | MICROCHIP | IC RFID R/W 125KHZ NOA3 MICROMOD |

获取价格 |

|

| ATA5577M1330C-PPMY | MICROCHIP | IC ID R/W TRANSPONDER PLASTIC |

获取价格 |

|

| ATA5577M1330C-UFQW | MICROCHIP | 125 KHZ IDIC (363BIT,R/W,330PF) |

获取价格 |

|

| ATA5577M133SC-DDB | MICROCHIP | IC RFID 125KHZ R/W 330PF BUMP |

获取价格 |

|

MAX3232 RS-232电平转换器资料手册参数分析

MAX3232 RS-232电平转换器资料手册参数分析

MAX485 RS-485/RS-422收发器资料手册参数分析

MAX485 RS-485/RS-422收发器资料手册参数分析

74HC245八路双向总线收发器:资料手册参数分析

74HC245八路双向总线收发器:资料手册参数分析

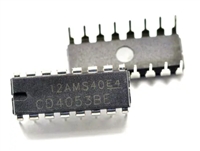

CD4053模拟多路复用器/解复用器:资料手册参数分析

CD4053模拟多路复用器/解复用器:资料手册参数分析