| 是否无铅: | 不含铅 | 是否Rohs认证: | 符合 |

| 生命周期: | Obsolete | 零件包装代码: | MODULE |

| 包装说明: | , | 针数: | 12 |

| Reach Compliance Code: | compliant | ECCN代码: | EAR99 |

| 风险等级: | 5.73 | 模拟集成电路 - 其他类型: | DC-DC REGULATED POWER SUPPLY MODULE |

| 最大输入电压: | 160 V | 最小输入电压: | 80 V |

| 标称输入电压: | 120 V | JESD-30 代码: | R-XDMA-P12 |

| 最大负载调整率: | 1% | 功能数量: | 1 |

| 输出次数: | 1 | 端子数量: | 12 |

| 最高工作温度: | 125 °C | 最低工作温度: | -55 °C |

| 最大输出电压: | 10.8 V | 标称输出电压: | 9 V |

| 封装主体材料: | UNSPECIFIED | 封装形状: | RECTANGULAR |

| 封装形式: | MICROELECTRONIC ASSEMBLY | 峰值回流温度(摄氏度): | 260 |

| 认证状态: | Not Qualified | 表面贴装: | NO |

| 技术: | HYBRID | 温度等级: | MILITARY |

| 端子形式: | PIN/PEG | 端子位置: | DUAL |

| 处于峰值回流温度下的最长时间: | 40 | 最大总功率输出: | 90 W |

| 微调/可调输出: | YES | Base Number Matches: | 1 |

| 型号 | 品牌 | 描述 | 获取价格 | 数据表 |

| AFL12009DW/HB | ETC | DC to DC Converter |

获取价格 |

|

| AFL12009DW-CH | INFINEON | ADVANCED ANALOG HIGH RELIABILITY HYBRID DC/DC CONVERTERS |

获取价格 |

|

| AFL12009DW-ES | INFINEON | ADVANCED ANALOG HIGH RELIABILITY HYBRID DC/DC CONVERTERS |

获取价格 |

|

| AFL12009DW-HB | INFINEON | ADVANCED ANALOG HIGH RELIABILITY HYBRID DC/DC CONVERTERS |

获取价格 |

|

| AFL12009DX | INFINEON | DC-DC Regulated Power Supply Module, 2 Output, 66W, Hybrid |

获取价格 |

|

| AFL12009DX/CH | ETC | DC to DC Converter |

获取价格 |

|

MC34063开关稳压器:全面参数解析与设计指南

MC34063开关稳压器:全面参数解析与设计指南

CC2530无线微控制器:资料手册参数分析

CC2530无线微控制器:资料手册参数分析

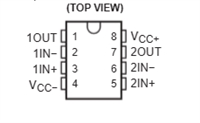

NE5532双低噪声运算放大器:资料手册参数分析

NE5532双低噪声运算放大器:资料手册参数分析

74LS138 3-to-8线解码器/多路复用器:资料手册参数分析

74LS138 3-to-8线解码器/多路复用器:资料手册参数分析