AD7878

ORDERING GUIDE

Signal-

DB10–DB8 (AFC2–AFC0)

Almost Full Word Count, Read/Write. The count value deter-

mines the number of words in the FIFO memory, which will

cause ALFL to be set. When the FIFO word count equals the

programmed count in these three bits, both the ALFL output

and DB11 of the status register are set to a logic low. For ex-

ample, when a code of 011 is written to these bits, ALFL is set

when Location 0 through Location 3 of the FIFO memory

contains valid data. AFC2 is the most significant bit of the word

count. The count value can be read back if required.

Data

Access

Time

Temperature

to-Noise

Ratio

Package

Options3

Model1, 2

Range

AD7878JN

0°C to +70°C

AD7878AQ –25°C to +85°C

AD7878SQ –55°C to +125°C

AD7878KN 0°C to +70°C

AD7878BQ –25°C to +85°C

AD7878LN 0°C to +70°C

AD7878SE4 –55°C to +125°C

70 dB

70 dB

70 dB

72 dB

72 dB

72 dB

70 dB

70 dB

72 dB

72 dB

57 ns

57 ns

57 ns

57 ns

57 ns

41 ns

57 ns

57 ns

57 ns

41 ns

N-28

Q-28

Q-28

N-28

Q-28

N-28

E-28A

P-28A

P-28A

P-28A

DB7 (ENAF)

AD7878JP

AD7878KP

AD7878LP

0°C to +70°C

0°C to +70°C

0°C to +70°C

Enable Almost Full, Read/Write. Writing a 1 to this bit disables

the ALFL output and status register bit DB11.

DB6 (FOVR/RESET)

NOTES

FIFO Overrun/RESET, Read/Write. Reading a 1 from this bit

indicates that at least one sample has been discarded because

the FIFO memory is full. When the FIFO is full (i.e., contains

eight words) any further conversion results will be lost. Writing

a 1 to this bit causes a system RESET as per the RESET input

(Pin 27).

1To order MIL-STD-883, Class B processed parts, add /883B to part number.

Contact our local sales office for military data sheet.

2Analog Devices reserves the right to ship either ceramic (D-28) packages or

cerdip (Q-28) hermetic packages.

3E = Leadless Ceramic Chip Carrier; N = Plastic DIP; P = Plastic Leaded Chip

Carrier, Q = Cerdip.

4Available to /883B processing only.

DB5 (FOOR/DISO)

STATUS/CONTROL REGISTER

FIFO Out of RANGE/Disable Outputs, Read/Write. Reading a

1 from this bit indicates that at least one sample in the FIFO

memory is out of range. Writing a 0 to this bit prevents the data

bus from becoming active while BUSY is low, regardless of the

state of CS and DMRD.

The status/control register serves the dual function of providing

control and monitoring the status of the FIFO memory. This

register is directly accessible through the data bus (DB11–DB0)

with a read or write operation while ADD0 is high. A write

operation to the status/control register provides control for the

ALFL output, bus interface and FIFO counter reset. This is

normally done on power-up initialization. The FIFO memory

address pointer is incremented after each conversion and com-

pared with a preprogrammed count in the status/control regis-

ter. When this preprogrammed count is reached, the ALFL

output is asserted if the ENAF control bit is set to zero. This

ALFL can be used to interrupt the microprocessor after any

predetermined number of conversions (between 1 and 8). The

status of the address pointer along with sample overrange and

ALFL status can be accessed at any time by reading the status/

control register. Note: reading the status/control register does

not cause any internal data movement in the FIFO memory.

Status information for a particular word should be read from the

status register before the data word is read from the FIFO

memory.

DB4 (FEMP)

FIFO Empty, Read Only. Reading a 1 indicates there are no

samples in the FIFO memory. When the FIFO is empty the

internal ripple-down effects of the FIFO are disabled and fur-

ther reads will continue to access the last valid data word in

Location 0.

DB3 (SOOR)

Sample out of Range, Read Only. Reading a 1 indicates the next

sample to be read is out of range, i.e., the sample in Location 0

of the FIFO.

DB–DB0 (FCN2–FCN0)

FIFO Word Count, Read Only. The value read from these bits

indicates the number of samples in the FIFO memory. For

example, reading 011 from these bits indicates that Location 0

through Location 3 contains valid data. Note: reading all 0s

indicates there is either one word or no word in the FIFO

memory; in this case the FIFO Empty determines if there is no

word in memory. FCN2 is the most significant bit.

STATUS/CONTROL REGISTER FUNCTION

DESCRIPTION

DB11 (ALFL)

Almost Full Flag, Read only. This is the same as Pin 6 (ALFL

output) status. A logic low indicates that the word count in

the FIFO memory has reached the preprogrammed count in bit

locations DB10–DB8. ALFL is updated at the end of conversion.

Table I. Status/Control Bit Function Description

DB11 DB10 DB9 DB8 DB7 DB6 DB5

AFC2 AFC1 AFC0 ENAF FOVR FOOR FEMP SOOR FCN2 FCN1 FCN0

BIT LOCATION

DB4

DB3

DB2

DB1

DB0

STATUS INFORMATION (READ)

CONTROL FUNCTION (WRITE)

RESET STATUS

ALFL

X

1

AFC2

0

AFC1

0

AFC0

0

ENAF RESET DISO

X

1

X

0

X

0

X

0

X

0

0

0

0

X =DON’T CARE

REV. A

–5–

MC34063开关稳压器:全面参数解析与设计指南

MC34063开关稳压器:全面参数解析与设计指南

CC2530无线微控制器:资料手册参数分析

CC2530无线微控制器:资料手册参数分析

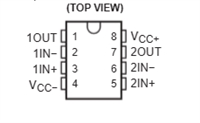

NE5532双低噪声运算放大器:资料手册参数分析

NE5532双低噪声运算放大器:资料手册参数分析

74LS138 3-to-8线解码器/多路复用器:资料手册参数分析

74LS138 3-to-8线解码器/多路复用器:资料手册参数分析