| 生命周期: | Active | 零件包装代码: | DIE |

| 包装说明: | DIE, | Reach Compliance Code: | compliant |

| ECCN代码: | EAR99 | HTS代码: | 8542.39.00.01 |

| 风险等级: | 5.59 | Is Samacsys: | N |

| 最大模拟输入电压: | 2.625 V | 最小模拟输入电压: | |

| 最长转换时间: | 15 µs | 转换器类型: | ADC, SUCCESSIVE APPROXIMATION |

| JESD-30 代码: | X-XUUC-N | 最大线性误差 (EL): | 0.0977% |

| 模拟输入通道数量: | 4 | 位数: | 10 |

| 功能数量: | 1 | 输出位码: | 2'S COMPLEMENT BINARY |

| 输出格式: | SERIAL | 封装主体材料: | UNSPECIFIED |

| 封装代码: | DIE | 封装形状: | UNSPECIFIED |

| 封装形式: | UNCASED CHIP | 认证状态: | Not Qualified |

| 采样并保持/跟踪并保持: | TRACK | 标称供电电压: | 3 V |

| 表面贴装: | YES | 端子形式: | NO LEAD |

| 端子位置: | UPPER | Base Number Matches: | 1 |

| 型号 | 品牌 | 描述 | 获取价格 | 数据表 |

| AD7417BR-REEL7 | ADI | 10-Bit Digital Temperature Sensor (AD7416) and Single/Four-Channel ADC (AD7417/AD7418) |

获取价格 |

|

| AD7417BRZ | ADI | 10-Bit Digital Temperature Sensor (AD7416) and Four Single-Channel ADCs |

获取价格 |

|

| AD7417BRZ-REEL | ADI | 10-Bit Digital Temperature Sensor (AD7416) and Four Single-Channel ADCs |

获取价格 |

|

| AD7417BRZ-REEL7 | ADI | 10-Bit Digital Temperature Sensor (AD7416) and Four Single-Channel ADCs |

获取价格 |

|

| AD7417R | ADI | Switch/Digital Output Temperature Sensor, DIGITAL TEMP SENSOR-SERIAL, 10BIT(s), 3Cel, RECT |

获取价格 |

|

| AD7417RU | ADI | Switch/Digital Output Temperature Sensor, DIGITAL TEMP SENSOR-SERIAL, 10BIT(s), 3Cel, RECT |

获取价格 |

|

MC34063开关稳压器:全面参数解析与设计指南

MC34063开关稳压器:全面参数解析与设计指南

CC2530无线微控制器:资料手册参数分析

CC2530无线微控制器:资料手册参数分析

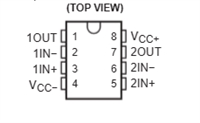

NE5532双低噪声运算放大器:资料手册参数分析

NE5532双低噪声运算放大器:资料手册参数分析

74LS138 3-to-8线解码器/多路复用器:资料手册参数分析

74LS138 3-to-8线解码器/多路复用器:资料手册参数分析