AD28msp02

The IIR low-pass filter is a 10th-order elliptic filter with a pass-

band edge at 3.70 kHz and a stopband attenuation of 65 dB at

4 kHz. This filter has the following specifications:

SERIAL PORT

The AD28msp02 communicates with a host processor via the

bidirectional synchronous serial port (SPORT). The SPORT is

used to transmit and receive digital data and control information.

Filter type:

l0th-order low-pass elliptic IIR

40.0 kHz

Sample frequency:

Passband cutoff:*

Passband ripple:

Stopband cutoff:

Stopband ripple:

All serial transfers are 16 bits long, MSB first. Data bits are

transferred at the serial clock rate (SCLK). SCLK equals the

master clock frequency divided by 5. SCLK = 2.6 MHz for the

master clock frequency MCLK = 13.0 MHz.

3.70 kHz

±0.2 dB

4.0 kHz

–65.00 dB

Host Processor Interface

*The passband cutoff frequency is defined to be the last point in the passband

that meets the passband ripple specification.

The AD28msp02-to-host processor interface is shown in Figure 4.

(Note that these specifications apply only to this filter, and not to the entire

DAC. The specifications can be used to perform further analysis of the exact

characteristics of the filter, for example using a digital filter design software

package.)

Host Processor

AD28msp02

SDO

SERIAL DATA RECEIVE

RECEIVE FRAME SYNC

SDOFS

Figure 2 shows the frequency response of the IIR low-pass filter.

SCLK

DATA/CNTRL

SERIAL CLOCK

FLAG

Passband ripple is ±0.2 dB for the combined effects of the

DAC’s digital filters (i.e., high-pass filter and IIR low pass of the

interpolation filter) in the 300 Hz–3400 Hz passband.

SDI

SDIFS

SERIAL DATA TRANSMIT

TRANSMIT FRAME SYNC

Analog Smoothing Filter and Programmable Gain Amplifier

The programmable gain amplifier (PGA) can be used to adjust

the output signal level by –15 dB to +6 dB. This gain is selected

by bits 7–9 (OG0, OG1, OG2) of the AD28msp02’s control

register.

Figure 4. AD28msp02-to-Host Processor Interface

Table I describes the SPORT signals and how they are used to

communicate with the host processor. The AD28msp02’s chip

select (CS) must be held high to enable SPORT operation. CS

can be used to 3-state the SPORT pins and disable communica-

tion with the host processor.

The AD28msp02’s analog smoothing filter consists of a 2nd-

order Sallen-Key continuous-time filter and a 3rd-order

switched capacitor filter. The Sallen-Key filter has a 3 dB point

at approximately 80 kHz.

To use the ADSP-2101 or ADSP-2111 as host DSP processor

for the AD28msp02, the following connections can be used (as

shown in Figure 5):

Differential Output Amplifier

The AD28msp02’s analog output (VOUTP, VOUTN) is pro-

duced by a differential output amplifier. The differential ampli-

fier can drive loads of 2 kΩ or greater and has a maximum

differential output voltage swing of ±3.156 V peak-to-peak

(3.17 dBm0). The output signal is dc-biased to the

AD28msp02’s on-chip voltage reference (VREF) and can be

ac-coupled directly to a load or dc-coupled to an external ampli-

fier. Refer to “Analog Output” in the “Design Considerations”

section of this data sheet for more information.

AD28msp02 Pin

ADSP-2101/2111 Pin

SCLK

SDO

SDOFS

SDI

SDIFS

–

–

–

–

–

–

SCLK0

DR0

RFS0

DT0

TFS0

DATA/CNTRL

FO (Flag Output)

The VOUTP–VOUTN outputs must be used as differential out-

puts; do not use either as a single-ended output.

Table I. SPORT Signals

Signal

Name

Signal State When

RESET Low (CS High)

Signal State During

Powerdown (CS High)

Description

Generated By

SCLK

SDO

SDOFS

SDI

Serial clock

Serial data output

Serial data output frame sync

Serial data input

Serial data input frame sync

AD28msp02

AD28msp02

AD28msp02

Host Processor

Host Processor

Low

Low

Low

—

Active

Active*

Low

—

SDIFS

—

—

(CS must be held high to enable SPORT operation.)

*Outputs last data value that was valid prior to entering powerdown.

–4–

REV. 0

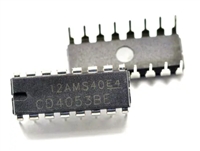

CD4053模拟多路复用器/解复用器:资料手册参数分析

CD4053模拟多路复用器/解复用器:资料手册参数分析

CD4011双4位二进制计数器:资料手册参数分析

CD4011双4位二进制计数器:资料手册参数分析

PCM1794音频DAC:全面参数解析与关键特性指南

PCM1794音频DAC:全面参数解析与关键特性指南

TLP250光耦合器:资料手册参数分析

TLP250光耦合器:资料手册参数分析