A49FL004

4 Mbit CMOS 3.3Volt-only Firmware Hub/LPC Flash Memory

Preliminary

FEATURES

• Single Power Supply Operation

Low voltage range: 3.0 V - 3.6 V

• Standard Intel Firmware Hub/LPC Interface

-

Standard SDP Command Set

-

-

-

-

Data Polling and Toggle Bit features

Block Locking Register for all blocks

Register-based read and write protection for

each block

4 ID pins for multiple chips selection

5 GPI pins for General Purpose Input Register

-

-

Read compatible to Intel® 82802 Firmware

Hub devices

Conforms to Intel LPC Interface Specification

Revision 1.1

-

-

• Memory Configuration

512K x 8 (4 Mbit)

• Block Architecture

-

-

TBL pin for hardware write protection to Boot Block

-

WP pin for hardware write protection to whole memory

array except Boot Block

-

-

-

Uniform 4 KBytes Sectors

Uniform 64 KByte overlay blocks

Support full chip erase for Address/Address

Multiplexed (A/A Mux) mode

• Address/Address Multiplexed (A/A Mux) Mode

-

-

-

11-pin multiplexed address and 8-pin data I/O interface

Supports fast programming on EPROM programmers

Standard SDP Command Set

• Automatic Erase and Program Operation

-

Build-in automatic program verification for extended

product endurance

-

Data Polling and Toggle Bit features

-

-

-

-

Typical 10 µs/byte programming time

Typical x s sector erase time

Typical y s block erase time

• Lower Power Consumption

-

-

Typical 12mA active read current

Typical 17mA program/erase current

Typical z s chip erase time

• High Product Endurance

• Two Configurable Interfaces

-

-

Guarantee 100,000 program/erase cycles per single

sector (preliminary)

Minimum 20 years data retention

-

In-System hardware interface: Auto detection of

Firmware Hub (FWH) or Low Pin Count (LPC)

Interface for in-system read and write operations

Address/Address Multiplexed (A/A Mux) Interface for

programming on EPROM Programmers during

manufacturing

• Compatible Pin-out and Packaging

-

-

-

-

32-pin (8 mm x 14 mm) TSOP

32-pin PLCC

Optional lead-free (Pb-free) package

• Firmware Hub (FWH)/Low Pin Count (LPC) Mode

• Hardware Data Protection

-

-

33 MHz synchronous operation with PCI bus

5-signal communication interface for in-system read

and write operations

PRELIMINARY

(September, 2005, Version 0.0)

1

AMIC Technology, Corp.

MC34063开关稳压器:全面参数解析与设计指南

MC34063开关稳压器:全面参数解析与设计指南

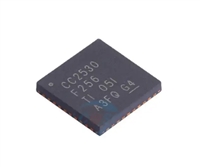

CC2530无线微控制器:资料手册参数分析

CC2530无线微控制器:资料手册参数分析

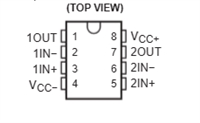

NE5532双低噪声运算放大器:资料手册参数分析

NE5532双低噪声运算放大器:资料手册参数分析

74LS138 3-to-8线解码器/多路复用器:资料手册参数分析

74LS138 3-to-8线解码器/多路复用器:资料手册参数分析