73S8024RN Data Sheet

DS_8024RN_020

MICROCONTROLLER INTERFACE

Name

Pin

Pin

Pin

Description

28SO

20QFN 32QFN

CMDVCC

19

10

20

18

Command VCC (negative assertion): Logic low on this pin

causes the LDO regulator to ramp the VCC supply to the

card and initiates a card activation sequence, if a card is

present.

5V/#V

3

31

5 volt / 3 volt card selection: Logic one selects 5 volts for

VCC and card interface, logic low selects 3 volt operation.

When the part is to be used with a single card voltage,

this pin should be tied to either GND or VDD. However, it

includes a high impedance pull-up resistor to default this

pin high (selection of 5V card) when not connected.

CLKSTOP

CLKLVL

7

8

–

–

4

5

Stops the card clock signal during a card session when

set high (card clock STOP mode). Internal pull-down

resistor allows this pin to be left as an open circuit if the

clock STOP mode is not used.

Sets the logic level of the card clock STOP mode when

the clock is de-activated by setting pin 7 high. Logic low

selects card STOP low. Logic high selects card STOP

high. Internal pull-down resistor allows this pin to be left

as an open circuit if the clock STOP mode is not used.

CLKDIV1

CLKDIV2

1

2

18

19

29

30

Sets the divide ratio from the XTAL oscillator (or external

clock input) to the card clock. These pins include

pull-down resistors.

CLKDIV1

CLKDIV2

CLOCK RATE

XTALIN/8

XTALIN/4

XTALIN/2

XTALIN

0

0

1

1

0

1

1

0

OFF

23

14

22

Interrupt signal to the processor. Active Low - Multi-

function indicating fault conditions and card presence.

Open drain output configuration. It includes an internal

21kΩ pull-up to VDD.

RSTIN

I/OUC

20

26

11

17

19

26

Reset Input: This signal is the reset command to the card.

System controller data I/O to/from the card. Includes a

pull-up resistor to VDD.

AUX1UC

AUX2UC

27

28

–

–

27

28

System controller auxiliary data I/O to/from the card.

Includes a pull-up resistor to VDD.

System controller auxiliary data I/O to/from the card.

Includes a pull-up resistor to VDD.

6

Rev. 1.8

MC34063开关稳压器:全面参数解析与设计指南

MC34063开关稳压器:全面参数解析与设计指南

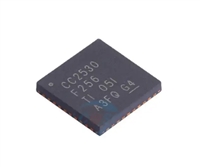

CC2530无线微控制器:资料手册参数分析

CC2530无线微控制器:资料手册参数分析

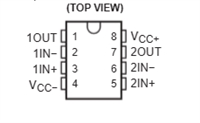

NE5532双低噪声运算放大器:资料手册参数分析

NE5532双低噪声运算放大器:资料手册参数分析

74LS138 3-to-8线解码器/多路复用器:资料手册参数分析

74LS138 3-to-8线解码器/多路复用器:资料手册参数分析