| 是否Rohs认证: | 符合 | 生命周期: | Transferred |

| 包装说明: | SIP, | Reach Compliance Code: | compliant |

| HTS代码: | 8542.39.00.01 | 风险等级: | 5.57 |

| 模拟集成电路 - 其他类型: | ANALOG CIRCUIT | JESD-30 代码: | R-CSIP-T2 |

| 长度: | 2.2095 mm | 功能数量: | 1 |

| 端子数量: | 2 | 最高工作温度: | 125 °C |

| 最低工作温度: | -55 °C | 封装主体材料: | CERAMIC, METAL-SEALED COFIRED |

| 封装代码: | SIP | 封装形状: | RECTANGULAR |

| 封装形式: | IN-LINE | 峰值回流温度(摄氏度): | NOT SPECIFIED |

| 认证状态: | Not Qualified | 筛选级别: | MIL-PRF-38535 Class Q |

| 座面最大高度: | 6.862 mm | 最大供电电压 (Vsup): | 31 V |

| 最小供电电压 (Vsup): | 4 V | 标称供电电压 (Vsup): | 5 V |

| 表面贴装: | NO | 技术: | BIPOLAR |

| 温度等级: | MILITARY | 端子形式: | THROUGH-HOLE |

| 端子位置: | SINGLE | 处于峰值回流温度下的最长时间: | NOT SPECIFIED |

| 总剂量: | 300k Rad(Si) V | 宽度: | 1.1555 mm |

| Base Number Matches: | 1 |

| 型号 | 品牌 | 描述 | 获取价格 | 数据表 |

| 5962F1422501VXC | STMICROELECTRONICS | TWO TERM VOLTAGE REFERENCE |

获取价格 |

|

| 5962F1422601VXC | RENESAS | QUAD OP-AMP, 250uV OFFSET-MAX, 1.5MHz BAND WIDTH, CDFP14, ROHS COMPLIANT, HERMETIC SEALED, |

获取价格 |

|

| 5962F1422602V9A | RENESAS | DUAL OP-AMP, 250uV OFFSET-MAX, 1.5MHz BAND WIDTH, UUC8, ROHS COMPLIANT, DIE-8 |

获取价格 |

|

| 5962F1820901VXC | TI | 耐辐射加固保障 (RHA)、QMLV、300krad、12 位、双通道 3.2GSPS 或 |

获取价格 |

|

| 5962F1820901VYF | TI | 耐辐射加固保障 (RHA)、QMLV、300krad、12 位、双通道 3.2GSPS 或 |

获取价格 |

|

| 5962F2021601VXC | TI | 具有 SEFI 监控套件的航天级 (QMLV-RHA) 10/100/1000 以太网 P |

获取价格 |

|

74HC245八路双向总线收发器:资料手册参数分析

74HC245八路双向总线收发器:资料手册参数分析

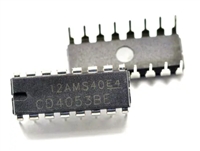

CD4053模拟多路复用器/解复用器:资料手册参数分析

CD4053模拟多路复用器/解复用器:资料手册参数分析

CD4011双4位二进制计数器:资料手册参数分析

CD4011双4位二进制计数器:资料手册参数分析

PCM1794音频DAC:全面参数解析与关键特性指南

PCM1794音频DAC:全面参数解析与关键特性指南