R

QPRO XQ4000XL Series QML High-Reliability FPGAs

XQ4000XL AC Switching Characteristic

Testing of the switching parameters is modeled after testing

methods specified by MIL-M-38510/605. All devices are

100% functionally tested. Internal timing parameters are

derived from measuring internal test patterns. Listed below

are representative values where one global clock input

drives one vertical clock line in each accessible column, and

where all accessible IOB and CLB flip-flops are clocked by

the global clock net.

driven from the same global clock, the delay is longer. For

more specific, more precise, and worst-case guaranteed

data, reflecting the actual routing structure, use the values

provided by the static timing analyzer (TRCE in the Xilinx

Development System) and back-annotated to the simulation

netlist. These path delays, provided as a guideline, have

been extracted from the static timing analyzer report. All

timing parameters assume worst-case operating conditions

(supply voltage and junction temperature)

When fewer vertical clock lines are connected, the clock dis-

tribution is faster; when multiple clock lines per column are

Global Buffer Switching Characteristics

-3

Max

3.6

4.8

6.3

-

-1

All

Min

Symbol

Description

Device

Max

Units

ns

T

Delay from pad through Global Low Skew buffer, to any

clock K

XQ4013XL

XQ4036XL

XQ4062XL

XQ4085XL

0.6

1.1

1.4

1.6

-

-

GLS

ns

-

ns

5.7

ns

Global Early BUFGEs 1, 2, 5, and 6 to IOB Clock Characteristics

-3

Max

2.4

3.1

4.9

-

-1

All

Min

Symbol

Description

Device

Max

Units

ns

T

Delay from pad through Global Early buffer, to any IOB

clock. Values are for BUFGEs 1, 2, 5 and 6.

XQ4013XL

XQ4036XL

XQ4062XL

XQ4085XL

0.4

0.3

0.3

0.4

-

-

GE

ns

-

ns

4.7

ns

Global Early BUFGEs 3, 4, 7, and 8 to IOB Clock Characteristics

-3

Max

2.4

4.7

5.9

-

-1

All

Min

Symbol

Description

Device

Max

Units

ns

T

Delay from pad through Global Early buffer, to any IOB

clock. Values are for BUFGEs 3, 4, 7 and 8.

XQ4013XL

XQ4036XL

XQ4062XL

XQ4085XL

0.7

0.9

1.2

1.3

-

-

GE

ns

-

ns

5.5

ns

DS029 (v1.3) June 25, 2000

www.xilinx.com

5

Product Specification

1-800-255-7778

74HC245八路双向总线收发器:资料手册参数分析

74HC245八路双向总线收发器:资料手册参数分析

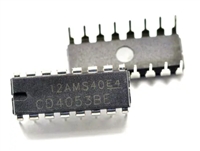

CD4053模拟多路复用器/解复用器:资料手册参数分析

CD4053模拟多路复用器/解复用器:资料手册参数分析

CD4011双4位二进制计数器:资料手册参数分析

CD4011双4位二进制计数器:资料手册参数分析

PCM1794音频DAC:全面参数解析与关键特性指南

PCM1794音频DAC:全面参数解析与关键特性指南