| 型号 | 品牌 | 描述 | 获取价格 | 数据表 |

| ST20-GP6 | STMICROELECTRONICS | GPS PROCESSOR |

获取价格 |

|

| ST20GP6CT33S | STMICROELECTRONICS | GPS PROCESSOR |

获取价格 |

|

| ST20GP6X33S | STMICROELECTRONICS | GPS PROCESSOR |

获取价格 |

|

| ST20-JPI | STMICROELECTRONICS | PC PARALLEL PORT TO JTAG INTERFACE |

获取价格 |

|

| ST20-JPI110 | STMICROELECTRONICS | PC PARALLEL PORT TO JTAG INTERFACE |

获取价格 |

|

| ST20-JPI-110 | STMICROELECTRONICS | PC PARALLEL PORT TO JTAG INTERFACE |

获取价格 |

|

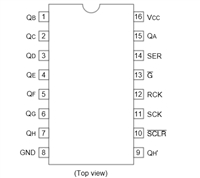

74HC595移位寄存器芯片:参数深入解析与应用实践指南

74HC595移位寄存器芯片:参数深入解析与应用实践指南

AO3401场效应管参数、引脚图、应用原理图

AO3401场效应管参数、引脚图、应用原理图

BT131可控硅参数及引脚图、工作原理详解

BT131可控硅参数及引脚图、工作原理详解

74LS32芯片参数、引脚图及功能真值表

74LS32芯片参数、引脚图及功能真值表