| 生命周期: | Obsolete | 零件包装代码: | BGA |

| 包装说明: | BGA, BGA304,23X23,50 | 针数: | 304 |

| Reach Compliance Code: | compliant | ECCN代码: | 3A991.A.2 |

| HTS代码: | 8542.31.00.01 | 风险等级: | 5.83 |

| 最大时钟频率: | 33 MHz | JESD-30 代码: | S-PBGA-B304 |

| 长度: | 31 mm | 端子数量: | 304 |

| 最高工作温度: | 70 °C | 最低工作温度: | |

| 封装主体材料: | PLASTIC/EPOXY | 封装代码: | BGA |

| 封装等效代码: | BGA304,23X23,50 | 封装形状: | SQUARE |

| 封装形式: | GRID ARRAY | 电源: | 3.3 V |

| 认证状态: | Not Qualified | 座面最大高度: | 2.54 mm |

| 子类别: | Bus Controllers | 标称供电电压: | 3.3 V |

| 表面贴装: | YES | 技术: | CMOS |

| 温度等级: | COMMERCIAL | 端子形式: | BALL |

| 端子节距: | 1.27 mm | 端子位置: | BOTTOM |

| 宽度: | 31 mm | uPs/uCs/外围集成电路类型: | BUS CONTROLLER, PCI |

| Base Number Matches: | 1 |

| 型号 | 品牌 | 描述 | 获取价格 | 数据表 |

| 21154BC | INTEL | PCI Bus Controller, CMOS, PBGA304, PLASTIC, BGA-304 |

获取价格 |

|

| 21154-BE | INTEL | PCI Bus Controller, CMOS, PBGA304, PLASTIC, BGA-304 |

获取价格 |

|

| 2115A | BELDEN | Fieldbus, 20 Pr #16 Str TC, XLPO Ins, IS/OS, TPE Jkt, CMG |

获取价格 |

|

| 2115A0031000 | BELDEN | Fieldbus, 20 Pr #16 Str TC, XLPO Ins, IS/OS, TPE Jkt, CMG |

获取价格 |

|

| 2115A0061000 | BELDEN | Fieldbus, 20 Pr #16 Str TC, XLPO Ins, IS/OS, TPE Jkt, CMG |

获取价格 |

|

| 2115B10M00000YCX | MICROSEMI | Sine Output Oscillator, |

获取价格 |

|

74LS74是什么芯片 74LS74引脚图及功能表

74LS74是什么芯片 74LS74引脚图及功能表

CD4511芯片引脚图及功能、电路图解析

CD4511芯片引脚图及功能、电路图解析

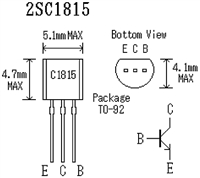

2SC1815三极管参数及引脚图功能详解

2SC1815三极管参数及引脚图功能详解

TL432和TL431有什么区别

TL432和TL431有什么区别