| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| ICS91857AG-LF | IDT |

获取价格 |

PLL Based Clock Driver, 91857 Series, 10 True Output(s), 0 Inverted Output(s), PDSO48, 6.1 |

|

| ICS91857AG-LF-T | IDT |

获取价格 |

PLL Based Clock Driver, 91857 Series, 10 True Output(s), 0 Inverted Output(s), PDSO48, 6.1 |

|

| ICS91857AG-T | IDT |

获取价格 |

91857 SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48, 6.1 |

|

| ICS91857AGT | IDT |

获取价格 |

PLL Based Clock Driver, 91857 Series, 10 True Output(s), 0 Inverted Output(s), PDSO48, 6.1 |

|

| ICS91857AGT | RENESAS |

获取价格 |

输入信号类型:LVCMOS;输出信号类型:SSTL-2;元器件封装:48-TSSOP; |

|

| ICS91857AL-T | IDT |

获取价格 |

91857 SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48, 4.4 |

|

| ICS91857ALLF | IDT |

获取价格 |

Clock Driver, PDSO48 |

|

| ICS91857ALLFT | IDT |

获取价格 |

Clock Driver, PDSO48 |

|

| ICS91857GLFT | IDT |

获取价格 |

Clock Driver |

|

| ICS91857LT | IDT |

获取价格 |

Clock Driver |

|

国产芯片新突破!南芯科技发布首颗全国产垂直集成高边开关

国产芯片新突破!南芯科技发布首颗全国产垂直集成高边开关

美方收取15%在华收入分成!英伟达AMD获批对华出口AI芯片

美方收取15%在华收入分成!英伟达AMD获批对华出口AI芯片

高性能计算推动封装革新:斥资20亿,国内半导体企业加快布局

高性能计算推动封装革新:斥资20亿,国内半导体企业加快布局

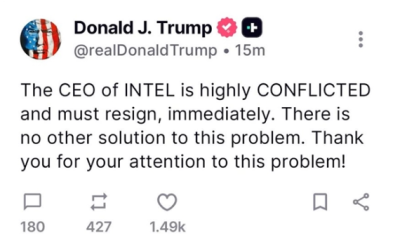

特朗普为何要求英特尔CEO陈立武立即辞职?利益冲突引股价震荡

特朗普为何要求英特尔CEO陈立武立即辞职?利益冲突引股价震荡