| 生命周期: | Transferred | 包装说明: | HVQCCN, |

| Reach Compliance Code: | unknown | HTS代码: | 8542.39.00.01 |

| 风险等级: | 5.8 | JESD-30 代码: | S-PQCC-N32 |

| 长度: | 5 mm | 功能数量: | 1 |

| 端子数量: | 32 | 最高工作温度: | 85 °C |

| 最低工作温度: | -40 °C | 封装主体材料: | PLASTIC/EPOXY |

| 封装代码: | HVQCCN | 封装形状: | SQUARE |

| 封装形式: | CHIP CARRIER, HEAT SINK/SLUG, VERY THIN PROFILE | 座面最大高度: | 1 mm |

| 标称供电电压: | 5 V | 表面贴装: | YES |

| 电信集成电路类型: | ATM/SONET/SDH SUPPORT CIRCUIT | 温度等级: | INDUSTRIAL |

| 端子形式: | NO LEAD | 端子节距: | 0.5 mm |

| 端子位置: | QUAD | 宽度: | 5 mm |

| Base Number Matches: | 1 |

| 型号 | 品牌 | 描述 | 获取价格 | 数据表 |

| HMC699LP5ETR | ADI | 7 GHz Integer-N Synthesizer SMT |

获取价格 |

|

| HMC699LP5RTR | HITTITE | PLL/Frequency Synthesis Circuit, |

获取价格 |

|

| HMC699LP5TR | HITTITE | Support Circuit, 1-Func, PQCC32, 5 X 5 MM, ROHS COMPLIANT, PLASTIC, SMT-32 |

获取价格 |

|

| HMC700LP4 | HITTITE | 8 GHz 16-Bit Fractional-N PLL |

获取价格 |

|

| HMC700LP4E | HITTITE | 8 GHz 16-Bit Fractional-N PLL |

获取价格 |

|

| HMC700LP4ERTR | HITTITE | PLL/Frequency Synthesis Circuit, |

获取价格 |

|

74LS74是什么芯片 74LS74引脚图及功能表

74LS74是什么芯片 74LS74引脚图及功能表

CD4511芯片引脚图及功能、电路图解析

CD4511芯片引脚图及功能、电路图解析

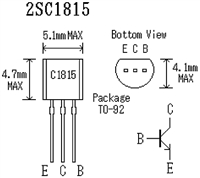

2SC1815三极管参数及引脚图功能详解

2SC1815三极管参数及引脚图功能详解

TL432和TL431有什么区别

TL432和TL431有什么区别