| 生命周期: | Active | 零件包装代码: | DIP |

| 包装说明: | CERAMIC, DIP-24 | 针数: | 24 |

| Reach Compliance Code: | compliant | ECCN代码: | 3A001.A.2.C |

| HTS代码: | 8542.39.00.01 | 风险等级: | 5.23 |

| Is Samacsys: | N | 其他特性: | ASYNCHRONOUS REGISTERED; 10 MACROCELLS; REGISTER PRELOAD; POWER-UP RESET |

| 架构: | PAL-TYPE | 最大时钟频率: | 25 MHz |

| JESD-30 代码: | R-GDIP-T24 | JESD-609代码: | e0 |

| 长度: | 31.877 mm | 专用输入次数: | 10 |

| I/O 线路数量: | 10 | 输入次数: | 20 |

| 输出次数: | 10 | 产品条款数: | 80 |

| 端子数量: | 24 | 最高工作温度: | 125 °C |

| 最低工作温度: | -55 °C | 组织: | 10 DEDICATED INPUTS, 10 I/O |

| 输出函数: | MACROCELL | 封装主体材料: | CERAMIC, GLASS-SEALED |

| 封装代码: | DIP | 封装等效代码: | DIP24,.3 |

| 封装形状: | RECTANGULAR | 封装形式: | IN-LINE |

| 电源: | 5 V | 可编程逻辑类型: | OT PLD |

| 传播延迟: | 25 ns | 认证状态: | Qualified |

| 筛选级别: | MIL-STD-883 | 座面最大高度: | 5.08 mm |

| 子类别: | Programmable Logic Devices | 最大供电电压: | 5.5 V |

| 最小供电电压: | 4.5 V | 标称供电电压: | 5 V |

| 表面贴装: | NO | 技术: | CMOS |

| 温度等级: | MILITARY | 端子面层: | TIN LEAD |

| 端子形式: | THROUGH-HOLE | 端子节距: | 2.54 mm |

| 端子位置: | DUAL | 宽度: | 7.62 mm |

| Base Number Matches: | 1 |

| 型号 | 品牌 | 描述 | 获取价格 | 数据表 |

| 5962-9055502LX | ETC | UV-Erasable/OTP PLD |

获取价格 |

|

| 5962-9055502XX | ETC | UV-Erasable/OTP PLD |

获取价格 |

|

| 5962-90555033A | WEDC | OT PLD, 20ns, CMOS, CQCC28, CERAMIC, LCC-28 |

获取价格 |

|

| 5962-90555033X | CYPRESS | OT PLD, 20ns, CMOS, CQCC28, CERAMIC, LCC-28 |

获取价格 |

|

| 5962-9055503KX | ETC | UV-Erasable/OTP PLD |

获取价格 |

|

| 5962-9055503LA | CYPRESS | OT PLD, 20ns, PAL-Type, CMOS, CDIP24, 0.300 INCH, CERDIP-24 |

获取价格 |

|

74LS74是什么芯片 74LS74引脚图及功能表

74LS74是什么芯片 74LS74引脚图及功能表

CD4511芯片引脚图及功能、电路图解析

CD4511芯片引脚图及功能、电路图解析

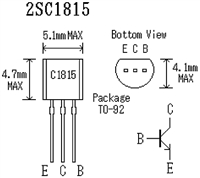

2SC1815三极管参数及引脚图功能详解

2SC1815三极管参数及引脚图功能详解

TL432和TL431有什么区别

TL432和TL431有什么区别