| 是否Rohs认证: | 不符合 | 生命周期: | Transferred |

| Reach Compliance Code: | unknown | 风险等级: | 5.64 |

| 最长访问时间: | 100 ns | 其他特性: | AUTOMATIC POWER-DOWN |

| I/O 类型: | COMMON | JESD-30 代码: | R-CZIP-T32 |

| JESD-609代码: | e0 | 内存密度: | 1048576 bit |

| 内存集成电路类型: | STANDARD SRAM | 内存宽度: | 8 |

| 功能数量: | 1 | 端口数量: | 1 |

| 端子数量: | 32 | 字数: | 131072 words |

| 字数代码: | 128000 | 工作模式: | ASYNCHRONOUS |

| 最高工作温度: | 125 °C | 最低工作温度: | -55 °C |

| 组织: | 128KX8 | 输出特性: | 3-STATE |

| 可输出: | YES | 封装主体材料: | CERAMIC, METAL-SEALED COFIRED |

| 封装代码: | ZIP | 封装等效代码: | ZIP32,.1 |

| 封装形状: | RECTANGULAR | 封装形式: | IN-LINE |

| 并行/串行: | PARALLEL | 电源: | 5 V |

| 认证状态: | Not Qualified | 最大待机电流: | 0.005 A |

| 最小待机电流: | 4.5 V | 子类别: | SRAMs |

| 最大压摆率: | 0.095 mA | 最大供电电压 (Vsup): | 5.5 V |

| 最小供电电压 (Vsup): | 4.5 V | 标称供电电压 (Vsup): | 5 V |

| 表面贴装: | NO | 技术: | CMOS |

| 温度等级: | MILITARY | 端子面层: | Tin/Lead (Sn/Pb) |

| 端子形式: | THROUGH-HOLE | 端子节距: | 1.27 mm |

| 端子位置: | ZIG-ZAG | Base Number Matches: | 1 |

| 型号 | 品牌 | 描述 | 获取价格 | 数据表 |

| EDI88128C100FM | WEDC | Standard SRAM, 128KX8, 100ns, CMOS, CDFP32, |

获取价格 |

|

| EDI88128C100LI | WEDC | Standard SRAM, 128KX8, 100ns, CMOS, CDSO32, CERAMIC, LCC-32 |

获取价格 |

|

| EDI88128C100LM | WEDC | Standard SRAM, 128KX8, 100ns, CMOS, CDSO32, CERAMIC, LCC-32 |

获取价格 |

|

| EDI88128C100NB | ETC | 128KX8 MONOLITHIC SRAM, SMD 5962-89598 |

获取价格 |

|

| EDI88128C100NC | WEDC | Standard SRAM, 128KX8, 100ns, CMOS, CDSO32, CERAMIC, SOJ-32 |

获取价格 |

|

| EDI88128C100NI | ETC | 128KX8 MONOLITHIC SRAM, SMD 5962-89598 |

获取价格 |

|

74LS74是什么芯片 74LS74引脚图及功能表

74LS74是什么芯片 74LS74引脚图及功能表

CD4511芯片引脚图及功能、电路图解析

CD4511芯片引脚图及功能、电路图解析

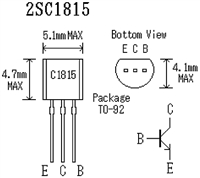

2SC1815三极管参数及引脚图功能详解

2SC1815三极管参数及引脚图功能详解

TL432和TL431有什么区别

TL432和TL431有什么区别