CY7C132, CY7C136

CY7C136A, CY7C142, CY7C146

2K x 8 Dual-Port Static RAM

Features

Functional Description

■ True dual-ported memory cells that enable simultaneous reads

of the same memory location

The CY7C132, CY7C136, CY7C136A, CY7C142, and CY7C146

are high speed CMOS 2K x 8 dual-port static RAMs. Two ports

are provided to permit independent access to any location in

memory. The CY7C132, CY7C136, and CY7C136A can be used

as either a standalone 8-bit dual-port static RAM or as a

MASTER dual-port RAM, in conjunction with the

CY7C142/CY7C146 SLAVE dual-port device. They are used in

systems that require 16-bit or greater word widths. This is the

solution to applications that require shared or buffered data, such

as cache memory for DSP, bit-slice, or multiprocessor designs.

■ 2K x 8 organization

■ 0.65 micron CMOS for optimum speed and power

■ High speed access: 15 ns

■ Low operating power: ICC = 110 mA (maximum)

■ Fully asynchronous operation

■ Automatic power down

Each port has independent control pins; chip enable (CE), write

enable (R/W), and output enable (OE). BUSY flags are provided

on each port. In addition, an interrupt flag (INT) is provided on

each port of the 52-pin PLCC version. BUSY signals that the port

is trying to access the same location currently being accessed

by the other port. On the PLCC version, INT is an interrupt flag

indicating that data is placed in an unique location (7FF for the

left port and 7FE for the right port).

■ MasterCY7C132/CY7C136/CY7C136A[1] easilyexpandsdata

bus width to 16 or more bits using slave CY7C142/CY7C146

■ BUSY output flag on CY7C132/CY7C136/CY7C136A;

BUSY input on CY7C142/CY7C146

■ INT flag for port to port communication (52-Pin PLCC/PQFP

versions)

An automatic power down feature is controlled independently on

each port by the chip enable (CE) pins.

■ CY7C136, CY7C136A, and CY7C146 available in 52-pin

PLCC and 52-pin PQFP packages

■ Pb-free packages available

Logic Block Diagram

R/W

L

R/W

R

CE

L

CE

R

OE

L

OE

R

I/O

I/O

I/O

I/O

7L

7R

I/O

CONTROL

I/O

CONTROL

0R

0L

[2]

[2]

BUSY

BUSY

R

L

A

A

A

10L

10R

0R

MEMORY

ARRAY

ADDRESS

DECODER

ADDRESS

DECODER

A

0L

ARBITRATION

LOGIC

(7C132/7C136 ONLY)

AND

INTERRUPTLOGIC

CE

L

CE

R

(7C136/7C146ONLY)

OE

L

OE

R

R/W

R/W

R

L

[3]

[3]

INT

L

INT

R

Notes

1. CY7C136 and CY7C136A are functionally identical.

2. CY7C132/CY7C136/CY7C136A (Master): BUSY is open drain output and requires pull up resistor. CY7C142/CY7C146 (Slave): BUSY is input.

3. Open drain outputs; pull up resistor required.

Cypress Semiconductor Corporation

Document #: 38-06031 Rev. *E

•

198 Champion Court

•

San Jose, CA 95134-1709

•

408-943-2600

Revised March 24, 2009

[+] Feedback

74LS74是什么芯片 74LS74引脚图及功能表

74LS74是什么芯片 74LS74引脚图及功能表

CD4511芯片引脚图及功能、电路图解析

CD4511芯片引脚图及功能、电路图解析

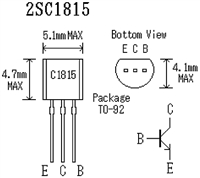

2SC1815三极管参数及引脚图功能详解

2SC1815三极管参数及引脚图功能详解

TL432和TL431有什么区别

TL432和TL431有什么区别